ITI LIMITED

Palakkad Plant, Kanjikode West

PALAKKAD - 678 623

KERALA -INDIA

Phone: (0491)2566010(4 Lines) Extn: 375,246,330 (0491) 2566180

E-Mail: pur3\_pkd@itiltd.co.in

Date: 13.10.2020

Ref: PN4901008

Dear Sir.

Sub: Request for Quote - Electronic Components

ITI Limited, Palakkad Plant requires 5Types Electronic Components for our AMC department. The Details of

| SI. No | Item Code     | Description                                                            | HSN         | Qty       |

|--------|---------------|------------------------------------------------------------------------|-------------|-----------|

| 1      | 501R000603    | SMD 0603 RES 1R00 1% 100PPM 50V 0.1W                                   | 85.42.31.00 | 5000 Nos. |

| 2      | 50331R0603    | SMD 0603 RES 331R 1% 100PPM 50V 0.1W                                   | 85.42.31.00 | 5000 Nos. |

| 3      | 50LM5026MTX   | LM5026 ACTIVE CLAMPCURRENT MODE PWM<br>CONTROLLER 16 PIN TSSOP PACKAGE | 85.42.31.00 | 250 Nos.  |

| 4      | 50MMBT3904LT1 | MMBT3904LT1 SOT-23 PLASTIC<br>ENCAPSULATED TRANSISTORS                 | 85.42.31.00 | 500 Nos.  |

| 5      | 50SI7898DP    | SI 7898 DP N-CHANNEL 150V (D-S) MOSFET<br>Power PAK SO-8 SINGLE        | 85.42.31.00 | 500 Nos.  |

Please submit your most competitive Offer for the above items showing the Item Code, Description, Date Code, Make, Part No, MOQ/MPQ etc in the following address in a sealed envelope to reach us on or before the due date on 21.10.2020 at 5.00 pm. E-mail quotes are also acceptable.

THE DEPUTY GENERAL MANAGER (MM)

ITI Ltd., Kanjikode West. P. O

Palakkad- 678 623, Tel: 0491 2566511.

The mail ID for general correspondence/queries / clarifications : pur3\_pkd@itiltd.co.in

### **GENERAL TERMS & CONDITIONS**

1. Terms of price

: At our Stores

2. Due date

: 21.10.2020 at 05.00 pm.

3. Tender opening date

: 22.10.2020 at 02.30 pm.

4. Validity of the quote

: 120 days.

5. Packing

: Standard packing

7. Payment

: 100 % within 90 days from date of delivery and Acceptance

8. Delivery

: Immediate

PLEASE INDICATE THE RFQ REFERENCE ,PN490I008 and DUE DATE i.e., 21-10-2020 - On top of the envelope of your quotation. *Quote should be in INR*. Please acknowledge the receipt of this enquiry by return mail. The interested bidders can participate in the tender opening.

Kindly attach copy of relevant documents if your firm is registered with MSME and NSIC for the availing the benefits extended to the MSEs.

Thanking You

Yours faithfully

C.USHA 19 Dy. Gen. Manager (MM)

Page: 1/6

LM5026

SNVS363E - AUGUST 2005-REVISED NOVEMBER 2015

# LM5026 Active Clamp Current Mode PWM Controller

## 1 Features

- Current-Mode Control

- · Internal 100-V Start-Up Bias Regulator

- 3-A Compound Main Gate Driver

- · High Bandwidth Optocoupler Interface

- Programmable Line Undervoltage Lockout (UVLO) With Adjustable Hysteresis

- Versatile Dual Mode Overcurrent Protection With Hiccup Delay Timer

- Programmable Overlap or Deadtime between the Main and Active Clamp Outputs

- Programmable Maximum Duty Cycle Clamp

- · Programmable Soft-Start

- · Leading Edge Blanking

- Resistor Programmed 1-MHz Capable Oscillator

- Oscillator Sync I/O Capability

- · Precision 5-V Reference

## 2 Applications

- · Server Power Supplies

- · 48-V Telecom Power Supplies

- High Efficiency DC-DC Power Supplies

## 3 Description

The LM5026 PWM controller contains all of the features necessary to implement power converters utilizing the active clamp and reset technique with current-mode control. With the active clamp technique, higher efficiencies and greater power densities can be realized compared to conventional catch winding or RDC clamp and reset techniques. Two control outputs are provided, the main power switch control (OUT\_A) and the active clamp switch control (OUT\_B). The device can be configured to control either a P-Channel or N-Channel clamp switch. The main gate driver features a compound configuration, consisting of both MOS and Bipolar devices, providing superior gate drive characteristics. The LM5026 can be configured to operate with bias voltages over a wide input range of 8 V to 100 V. Additional features include programmable maximum duty cycle, line undervoltage lockout, cycle-by-cycle current limit, hiccup mode fault operation with adjustable timeout delay, PWM slope compensation, 1-MHz capable oscillator synchronization input and output capability, precision reference, and thermal shutdown.

## Device Information(1)

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |  |  |

|-------------|------------|-------------------|--|--|

| LM5026      | WSON (16)  | 5.00 mm × 5.00 mm |  |  |

| LIVISOZO    | TSSOP (16) | 4.40 mm × 5.00 mm |  |  |

For all available packages, see the orderable addendum at the end of the data sheet.

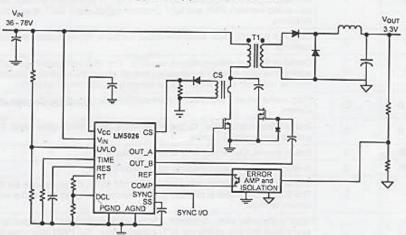

### Typical Application Circuit

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers, PRODUCTION DATA,

1/2

Page: 2/6

www.tl.com

LM5026

SNVS363E - AUGUST 2005-REVISED NOVEMBER 2015

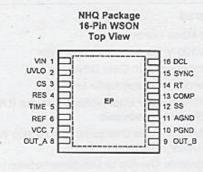

## 5 Pin Configuration and Functions

#### Pin Functions

| PIN TYPE(II |       |         |                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-------------|-------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NO.         | NAME  | TYPE(1) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 1           | VIN   | - 1     | Input voltage source. Input to the start-up regulator. Operating input range is 13 V to 100 V with transient capability to 105 V. For power sources outside of this range, the LM5026 can be biased directly at VCC by an external regulator.                                                                                                                                                                   |  |  |  |  |  |

| 2           | UVLO  | 1       | Line undervoltage lockout. An external voltage divider from the power source sets the shutdown and standby comparator levels. When UVLO reaches the 0.4-V threshold the VCC and REF regulators are enabled. At the 1.25-V threshold the SS pin is released and the device enters the active mode.                                                                                                               |  |  |  |  |  |

| 3           | cs    | 1       | Current Sense input for current mode control and current limit. If CS exceeds 0.5 V, the output pulse will be terminated, entering cycle-by-cycle current limit. An internal switch holds CS low for 100 nS after OUT_A switches high to blank leading edge transients.                                                                                                                                         |  |  |  |  |  |

| 4           | RES   | 1       | Restart Timer. If cycle-by-cycle current limit is reached during any cycle, a 10- $\mu$ A current is sourced to the RES pin capacitor. If the RES capacitor voltage reaches 2.5 V, the soft-start capacitor will be fully discharged and then released with a pullup current of 1 $\mu$ A. After the first output pulse at OUT_A (when SS = 1.4 V), the SS pin charging current will revert back to 50 $\mu$ A. |  |  |  |  |  |

| 5           | TIME  | 1       | Gate drive overlap or deadtime control. An external resistor (RSET) sets either the overlap time or deadtime for the active clamp output. An RSET resistor connected between TIME and AGND produces in-phase OUT_A and OUT_B pulses with overlap. An RSET resistor connected between TIME and REF produces out-of-phase OUT_A and OUT_B pulses with deadtime.                                                   |  |  |  |  |  |

| 6           | REF   | 0       | Output of 5-V reference. Maximum output current is 10 mA. Locally decouple with a 0.1-µF capacitor.                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 7           | vcc   | Р       | Output of the high voltage start-up regulator. The VCC voltage is regulated to 7.6 V. If an auxiliary winding raises the voltage on this pin above the regulation setpoint, the internal start-up regulator will shutdown, thus reducing the IC power dissipation.                                                                                                                                              |  |  |  |  |  |

| 8           | OUT_A | 0       | Main output driver. Output of the main switch PWM gate driver. Capable of 3-A peak sink current.                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 9           | OUT_B | 0       | Active clamp output driver. Output of the active clamp switch gate driver. Capable of 0.5-A peak source and sink current.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 10          | PGND  | G       | Power ground. Connect directly to analog cround.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 11 1        | AGND  | G       | Analog return. Connect directly to power cround.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 12          | SS.   | ì       | Soft-start. An external capacitor and an internal 50-µA current source set the soft-start ramp. The SS current source is reduced to 1 µA following a restart event. The soft-stop discharge current is 50 µA.                                                                                                                                                                                                   |  |  |  |  |  |

| 13          | COMP  | 1       | Input to the pulse width modulator. The external optocoupler connected to the COMP pin sources current into an internal NPN current mirror. The PWM duty cycle is maximum with zero input current, while 1 mA reduces the duty cycle to zero. The current mirror improves the frequency response by reducing the ac voltage across the optocoupler detector.                                                    |  |  |  |  |  |

(1) P = Power, G = Ground, I = Input, O = Output, I/O = Input/Output

Copyright @ 2005-2015, Texas Instruments Incorporated

Submit Documentation Feedback

3

Product Folder Links: LM5026

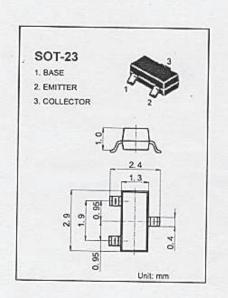

# **MMBT3904LT1**

# SOT-23 Plastic-Encapsulate Transistors

## MMBT3904LT1 TRANSISTOR (NPN)

## FEATURES

Power dissipation

P<sub>CM</sub>:

0.2

W (Tamb=25°C)

Collector current

ICM:

0.2

Collector-base voltage

V<sub>(BR)CBO</sub>:

60 V

Operating and storage junction temperature range

T<sub>J</sub>, T<sub>stg</sub>: -55°C to +150°C

# ELECTRICAL CHARACTERISTICS (Tamb=25°C unless otherwise specified)

| Parameter                            | Symbol                | Test conditions                                          | MIN | MAX  | UNIT |

|--------------------------------------|-----------------------|----------------------------------------------------------|-----|------|------|

| Collector-base breakdown voltage     | V <sub>(BR)CBO</sub>  | Ic= 100 μA, I <sub>E</sub> =0                            | 60  |      | V    |

| Collector-emitter breakdown voltage  | V <sub>(BR)CEO</sub>  | Ic= 1 mA, I <sub>B</sub> =0                              | 40  |      | V    |

| Emitter-base breakdown voltage       | V <sub>(BR)EBO</sub>  | I <sub>E</sub> = 100μA, I <sub>C</sub> =0                | 6   |      | V    |

| Collector cut-off current            | Ісво                  | V <sub>C8</sub> = 60V, I <sub>E</sub> =0                 |     | 0.1  | μА   |

| Collector cut-off current            | I <sub>CEO</sub>      | V <sub>CE</sub> = 40V, I <sub>B</sub> =0                 |     | 0.1  | μА   |

| Emitter cut-off current              | I <sub>EBO</sub>      | V <sub>EB</sub> = 5V, I <sub>C</sub> =0                  |     | 0.1  | μА   |

| DC current gain                      | H <sub>FE(1)</sub>    | V <sub>CE</sub> =10V, I <sub>C</sub> = 1mA               | 100 | 300  |      |

|                                      | H <sub>FE(2)</sub>    | V <sub>CE</sub> = 1V, I <sub>C</sub> = 50mA              | 60  |      |      |

| Collector-emitter saturation voltage | V <sub>CE</sub> (sat) | I <sub>C</sub> =50mA, I <sub>B</sub> = 5mA               |     | 0.3  | ٧    |

| Base-emitter saturation voltage      | V <sub>BE</sub> (sat) | I <sub>C</sub> = 50mA, I <sub>B</sub> = 5mA              |     | 0.95 | ٧    |

| Transition frequency                 | f <sub>T</sub>        | V <sub>CE</sub> = 20V, I <sub>C</sub> = 10mA<br>f=100MHz | 250 |      | MHz  |

| Delay Time                           | td                    | Vcc=3.0Vdc, VBE=-0.5Vdc                                  |     | 35   | nS   |

| Rise Time                            | tr                    | I <sub>C</sub> =10mAdc, I <sub>B1</sub> =1.0mAdc         |     | 35   | nS   |

| Storage Time                         | ts                    | Vcc=3.0Vdc, Ic=10mAdc                                    |     | 200  | nS   |

| Fall Time                            | tf                    | I <sub>81</sub> =I <sub>82</sub> =1.0mAdc                |     | 50   | nS   |

## **DEVICE MARKING**

MMBT3904LT1=1AM

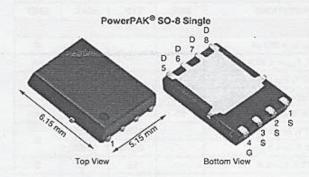

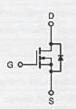

Si7898DP

FREE

Vishay Siliconix

## N-Channel 150 V (D-S) MOSFET

| PRODUCT SUMMARY                                           |   |        |

|-----------------------------------------------------------|---|--------|

| Vos (V)                                                   |   | 150    |

| $R_{OS(on)}$ max. ( $\Omega$ ) at $V_{GS} = 10 \text{ V}$ |   | 0.085  |

| $R_{DS(on)}$ max. ( $\Omega$ ) at $V_{GS} = 6 \text{ V}$  |   | 0.095  |

| Q <sub>a</sub> typ. (nC)                                  |   | 17     |

| I <sub>D</sub> (A)                                        |   | 4.8    |

| Configuration                                             | * | Single |

### **FEATURES**

- TrenchFET<sup>®</sup> power MOSFETs for fast switching

- New low thermal resistance PowerPAK<sup>®</sup> package with low 1.07 mm profile

- PWM optimized

- 100 % R<sub>g</sub> tested

- Material categorization: for definitions of compliance please see <a href="https://www.vishay.com/doc?99912">www.vishay.com/doc?99912</a>

# APPLICATIONS

- DC/DC power supply primary side switch

- · Industrial motor drives

N-Channel MOSFET

| ORDERING INFORMATION            |                 |

|---------------------------------|-----------------|

| Package                         | PowerPAK SO-8   |

| Lead (Pb)-free                  | Si7898DP-T1-E3  |

| Lead (Pb)-free and halogen-free | Si7898DP-T1-GE3 |

| PARAMETER                                                                |                        | SYMBOL          | 10 s        | STEADY STATE | UNIT |  |

|--------------------------------------------------------------------------|------------------------|-----------------|-------------|--------------|------|--|

| Drain-source voltage                                                     |                        | V <sub>DS</sub> | 150         | 150          | v    |  |

| Gate-source voltage                                                      |                        | V <sub>GS</sub> | ± 20        | ± 20         | V    |  |

| Continuous drain current ( $T_J = 150$ °C) a $T_A = 25$ °C $T_A = 70$ °C |                        | lo –            | 4.8         | 3            |      |  |

|                                                                          |                        |                 | 3.8         | 2.4          | А    |  |

| Pulsed drain current                                                     |                        | I <sub>DM</sub> | 25          | 25           |      |  |

| Avalanche current L = 0.1 mH                                             |                        | las             | 10          | 10           |      |  |

| Continuous source current (diode conducti                                | on) a -                | Is              | 4.1         | 1.6          |      |  |

|                                                                          | T <sub>A</sub> = 25 °C |                 | 5           | 1.9          | w    |  |

| Maximum power dissipation a T <sub>A</sub> = 70 °C                       |                        | Po              | 3.2         | 1.2          | W    |  |

| Operating junction and storage temperature range                         |                        | TJ, Tstg        | -55 to +150 |              | °C   |  |

| Soldering recommendations (peak temperature) b, c                        |                        |                 |             | 260          |      |  |

| THERMAL RESISTANCE RA            | TINGS        |                   |         |         |      |  |

|----------------------------------|--------------|-------------------|---------|---------|------|--|

| PARAMETER                        |              | SYMBOL            | TYPICAL | MAXIMUM | UNIT |  |

|                                  | t ≤ 10 s     | R <sub>thJA</sub> | 20      | 25      | °C/W |  |

| Maximum junction-to-ambient a    | Steady state |                   | 52      | 65      |      |  |

| Maximum junction-to-case (drain) | Steady state | R <sub>thJC</sub> | 2.1     | 2.6     |      |  |

### Notes

- a. Surface mounted on 1" x 1" FR4 board

- b. See solder profile (<u>www.vishay.com/doc?73257</u>). The PowerPAK SO-8 is a leadless package. The end of the lead terminal is exposed copper (not plated) as a result of the singulation process in manufacturing. A solder fillet at the exposed copper tip cannot be guaranteed and is not required to ensure adequate bottom side solder interconnection

- c. Rework conditions: manual soldering with a soldering iron is not recommended for leadless components

S09-0227-Rev. D, 09-Feb-09

Document Number: 71873

For technical questions, contact: pmostechsupport@vishay.com

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

#2

Spec: SL.No.5

www.vishay.com

Si7898DP

Vishay Siliconix

| PARAMETER                           | SYMBOL                | TEST CONDITIONS                                                        | MIN. | TYP.  | MAX.  | UNIT |  |

|-------------------------------------|-----------------------|------------------------------------------------------------------------|------|-------|-------|------|--|

| Static                              |                       |                                                                        |      |       |       |      |  |

| Gate threshold voltage              | V <sub>GS(th)</sub>   | V <sub>DS</sub> = V <sub>GS</sub> , I <sub>D</sub> = 250 μA            | 2    | -     | 4     | ٧    |  |

| Gate-body leakage                   | l <sub>GSS</sub>      | V <sub>DS</sub> = 0 V, V <sub>GS</sub> = ± 20 V                        |      |       | ± 100 | nA   |  |

| Zero gate voltage drain current     |                       | V <sub>DS</sub> = 150 V, V <sub>GS</sub> = 0 V                         |      |       | 1     |      |  |

| zero gate voltage drain current     | loss                  | V <sub>DS</sub> = 150 V, V <sub>GS</sub> = 0 V, T <sub>J</sub> = 55 °C | 5    |       |       | μА   |  |

| On-state drain current <sup>a</sup> | l <sub>D(on)</sub>    | V <sub>DS</sub> ≥5 V, V <sub>GS</sub> = 10 V                           | 25   |       |       | Α    |  |

| Drain-source on-state resistance a  | R <sub>DS(on)</sub>   | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 3.5 A                         |      | 0.068 | 0.085 | Ω    |  |

| brain-source on-state resistance -  |                       | V <sub>GS</sub> = 6 V, I <sub>D</sub> = 3 A                            |      | 0.076 | 0.095 |      |  |

| Forward transconductance *          | 9fs                   | V <sub>DS</sub> = 15 V, I <sub>D</sub> = 5 A                           | -    | 15    |       | S    |  |

| Diode forward voltage a             | V <sub>SD</sub>       | I <sub>S</sub> = 2.5 A, V <sub>GS</sub> = 0 V                          | -    | 0.75  | 1.2   | V    |  |

| Dynamic <sup>b</sup>                |                       |                                                                        |      | w     |       |      |  |

| Total gate charge                   | Qg                    |                                                                        | +    | 17    | 21    |      |  |

| Gate-source charge                  | Ogs                   | $V_{DS} = 75 \text{ V}, V_{GS} = 10 \text{ V}, I_D = 3.5 \text{ A}$    | -    | 3.2   | -     | nC   |  |

| Gate-drain charge                   | Q <sub>gd</sub>       |                                                                        | -    | 6     | -     |      |  |

| Gate resistance                     | Rg                    |                                                                        | 0.5  | 0.85  | 2.5   | Ω    |  |

| Turn-on delay time                  | t <sub>d(on)</sub>    |                                                                        | -    | 9     | 14    |      |  |

| Rise time                           | tr                    | $V_{DD} = 75 \text{ V}, R_L = 21 \Omega$                               |      | 10    | 15    |      |  |

| Turn-off delay time                 | . t <sub>d(off)</sub> | $I_D \equiv 3.5 \text{ A}, V_{GEN} = 10 \text{ V}, R_g = 6 \Omega$     | -    | 24    | 35    | ns   |  |

| Fall time                           | tf                    |                                                                        |      | 17    | 25    |      |  |

| Source-drain reverse recovery time  | t <sub>rr</sub>       | I <sub>F</sub> = 2.5 A, di/dt = 100 A/µs                               |      | 45    | 70    |      |  |

### Notes

- a. Pulse test: pulse width ≤ 300 µs, duty cycle ≤ 2 %

- b. Guaranteed by design, not subject to production testing

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

S09-0227-Rev. D, 09-Feb-09

Document Number: 71873